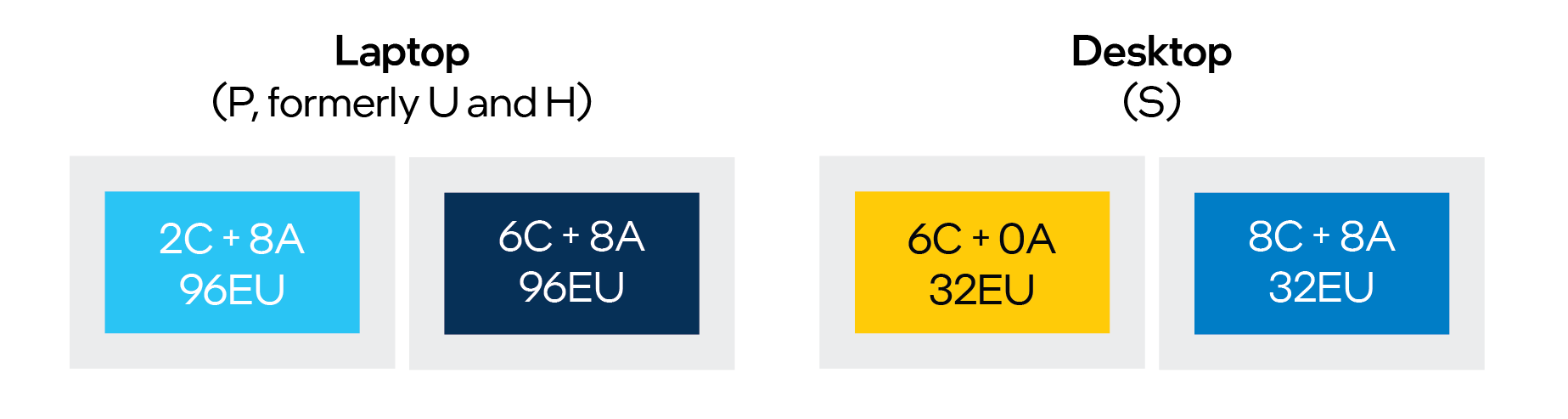

In the released developer manual, Intel has provided additional technical details about the new AlderLake CPU and special configurations. In addition to the variations already mentioned in the rumors for the desktop without “nuclear cores”, the notebook line has also been confirmed. There are other small details as well.

Of The developer manual is available on the Intel website So available to everyone. It is expected to release on October 27th, thus revealing some more in-depth details at some point.

Among other things, Intel actually planned to be able to deliver AVX-512 performance cores (B-cores) when performance cores (e-cores) are disabled — as the guide still calls it today. Because P-Cores or Golden Cove masters this function because they are used in the server environment.

But since the supported features are based on a less common class, like the predecessor Lockfield, in this case the power cores, the feature will be disabled on the desktop and notebook. Eventually, as the manufacturer announced on Alder Lake’s Architecture Day, Intel decided that even if the e-cores malfunctioned, the desktop would not have this function.

Hardware planning is a big topic

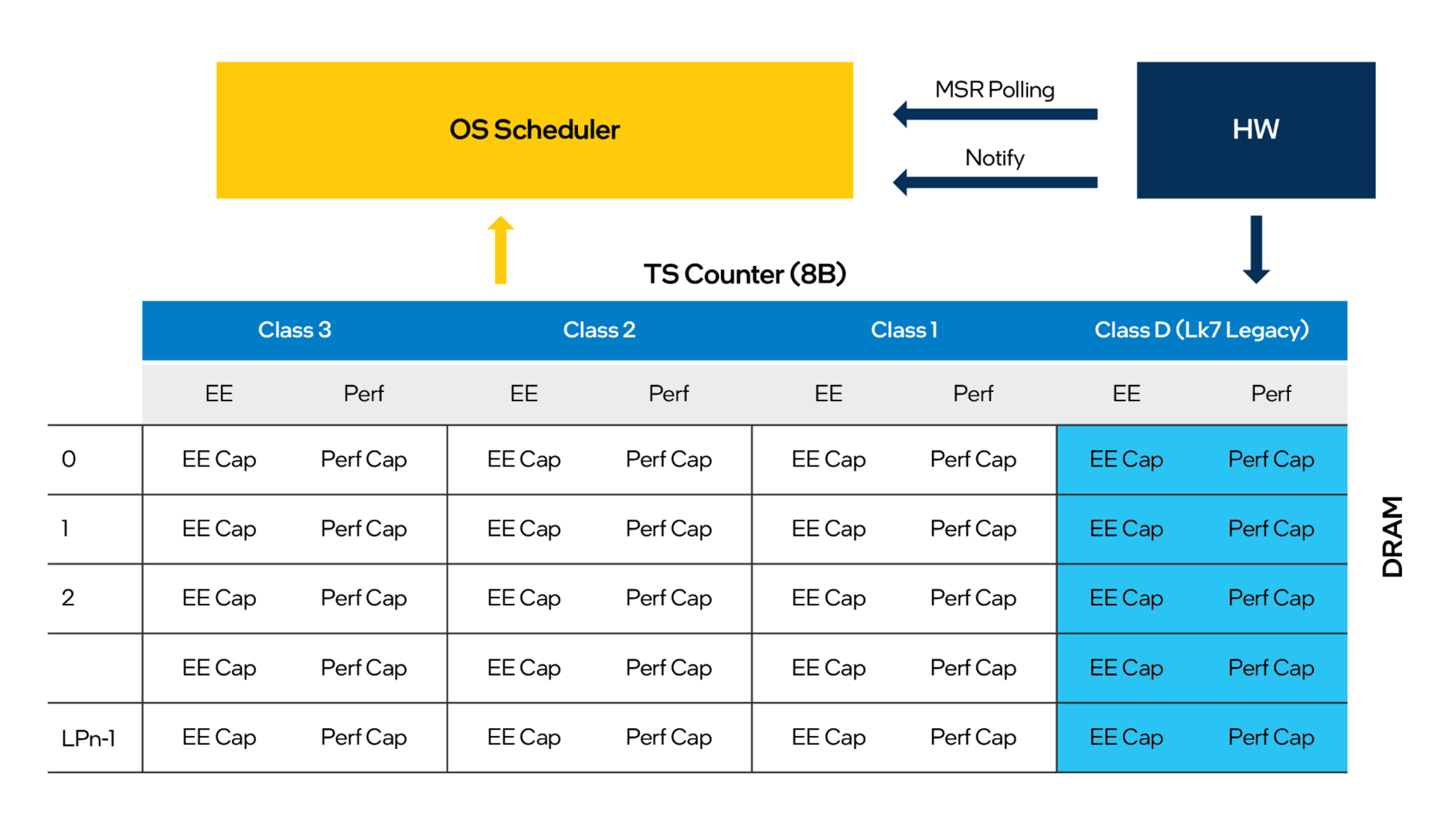

Much of the wizard is dedicated to the new Intel Thread Director (IDT), a hardware scheduler, which provides the task of providing intelligent specifications on which hub or thread on which operating system to perform best. Several parameters are taken into account.

Notes:

Each class of ID and Perf capabilities provides LP performance and comparative performance levels of efficient cores. Higher values here mean higher performance. For class ID, EE capacity provides the relative energy efficiency level of an LP. Higher values here indicate higher EE for texts with energy efficiency requirements. Depending on parameters such as power policy, battery slider, you can choose between OS EE and performance.

Different classes here refer to performance differences between cores. For example, Class 1 refers to ISAs such as AVX2-FP32, where P-cores provide higher performance than E-cores, while Class 2 refers to higher VNNI performance differentiation. Intel has also introduced a class to monitor waiting periods such as UMWAIT / TPAUSE, so performance cores do not sit idly by and go to real work efficient cores.

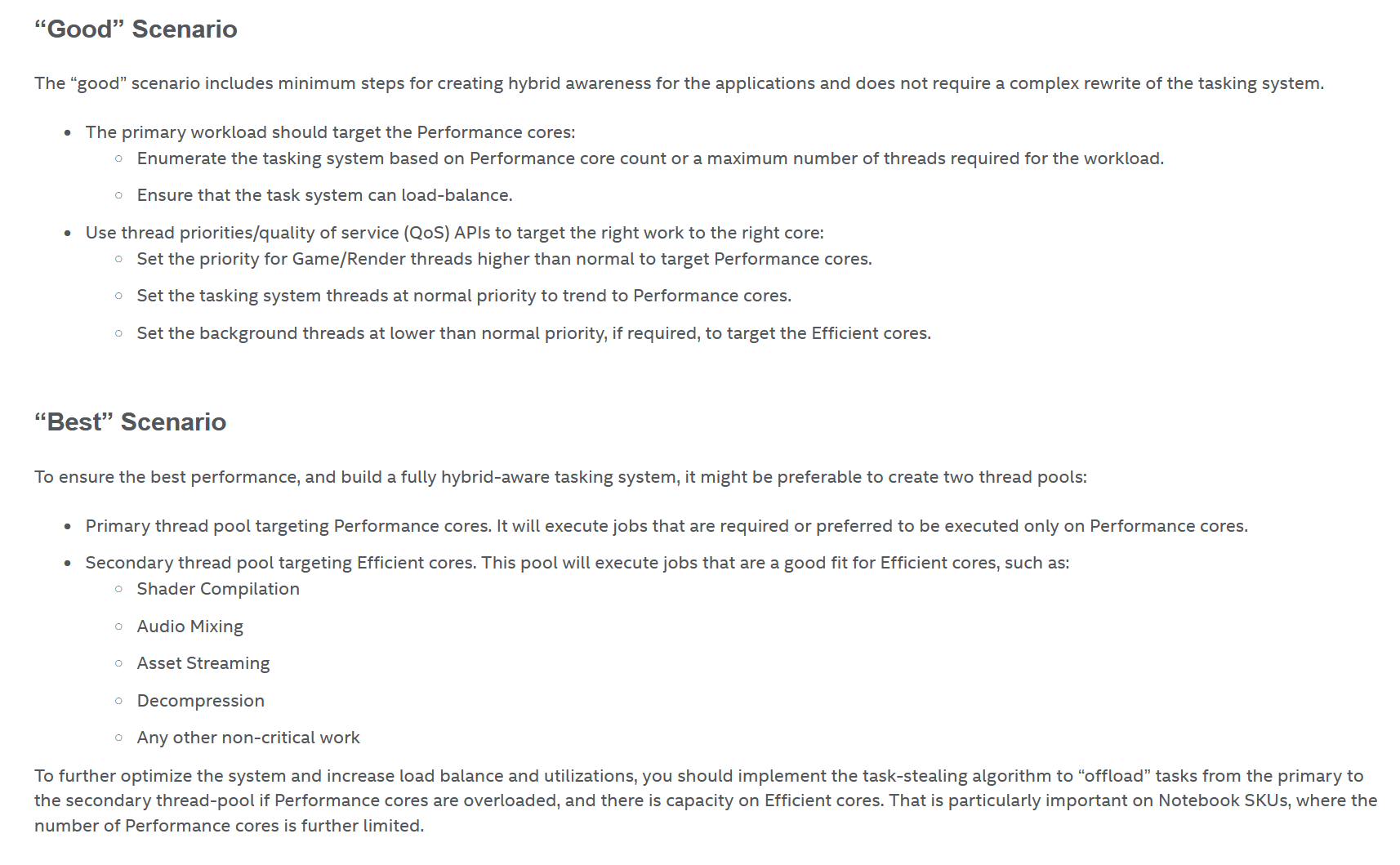

The guide also provides instructions on how to implement good and optimal profiles. Primarily the developer can decide which applications should run on e-cores. If it is only implemented in a basic way, AlderLake acts like a normal processor with many threads, which is guided by the operating system, gives erroneous tasks here and there and the cores are not used optimally or overhead forms, ultimately not indicating optimal performance.

Even on the desktop without the atom

Intel has already officially named three different CPU dies, and now the AlderLake-S desktop variant is also clear, which does not use e-cores. It can be used on the Core i5-12400F, among other things, the fourth processor of the Core models is always well positioned in their segment and there is no competition after the Core i5-9400F.

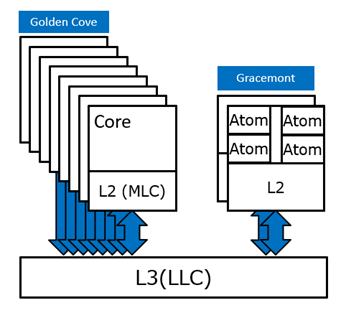

Core i5 in this class can then access the entire L3 cache and not share it with E-Cores – they are actually called Atom (A) in Intel. As the map and guide re-clarify, only the L3 cache is shared, and all other resources are available independently of the cores or core cluster in Greasmond.

Eventually tests will show what the Alter Lake-S can actually do. Intel has raised the bar with a 19 percent higher performance forecast than Rocket Lake, so expectations are falling accordingly. This will finally be clarified in early November.

“Avid writer. Subtly charming alcohol fanatic. Total twitter junkie. Coffee enthusiast. Proud gamer. Web aficionado. Music advocate. Zombie lover. Reader.”

More Stories

Acrylic Nails for the Modern Professional: Balancing Style and Practicality

The Majestic Journey of the African Spurred Tortoise: A Guide to Care and Habitat

Choosing Between a Russian and a Greek Tortoise: What You Need to Know